SIGNAL INTEGRITY ANALYSIS

Advancements in high-performance microprocessors and access to high-speed internet is driving the need for compact, high-

performance systems that offers reliable data transmission with superior signal integrity.

Signal Integrity Analysis

- High-speed serial/parallel interface analysis and design guidelines (NAND Flash, DDR3, DDR4, multi- gigabit Serdes, PCIe Gen3, Gen4 & 5 XAUI, PAM4, LPDDR4x, HDMI, SATA, USB 3.0, USB 4.0, Flash, chip-to-chip IO, FPGA IO)

- 25Gbps,56Gbps and Different Ethernet standards

- COM Simulations and their metrics

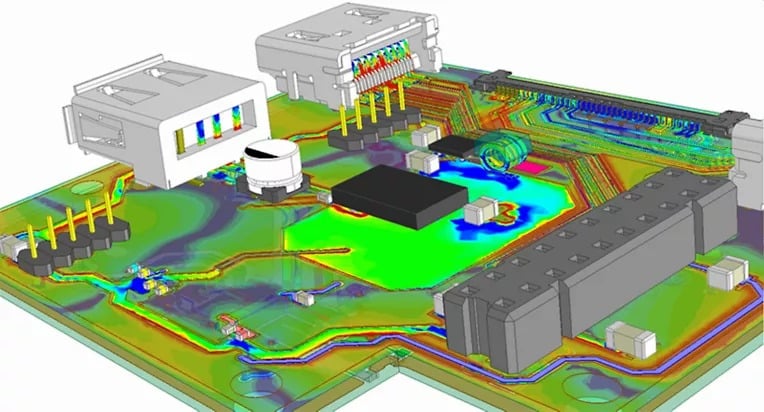

- Signal integrity & power integrity co-design SSN modelling

- Pre-layout & post-layout SI analysis

- IBIS/IBIS-AMI-based system-level SI evaluation

- Routing studies, termination schemes, stack-up design & analysis

- Trace & Via design for controlled impedance using EM solver

- Full-wave EM modelling of all kinds of interconnects (via, connector, end-to-end channel)

- Reflection, ringing and overshoot/undershoot

- Signal attenuation due to IR-Drop, skin-effect and dielectric loss

- Channel analysis for serial communication - eye diagram analysis

- Clock analysis (common & source synchronous)

- DDR timing analysis

- S parameter analysis

- Return & insertion loss, NEXT and FEXT analysis

- Mixed mode analysis channel (common & differential)

- Coupling analysis - Single and differential

- Co - design (IC/package/board)

- Crosstalk and s-parameter modelling of traces and interconnects on the package and board

- Connector design modelling and simulation

- IBIS model generation

Tools

- ANSYS HFSS™

- Synopsys HSPICE®

- Mentor Graphics® HyperLynx®

- ANSYS SIwave

- Keysight ADS

- Cadence Sigrity

- Intel - ICAT

We provide comprehensive system-level SI/PI simulation services at IC,

Package & PCB level and can resolve any complex SI/PI issues.